闩锁测试(Latch-up)

提供完整的半导体产品芯片可靠性试验项目,协助客户通过JEDEC、MIL—STD、AEC-Q等可靠性国际试验标准

提供完整的半导体产品芯片可靠性试验项目,协助客户通过JEDEC、MIL—STD、AEC-Q等可靠性国际试验标准

什么是闩锁测试

所谓的闩锁效应Latch-up,是指瞬间电流被锁定或者放大,而造成芯片在电源与对地之间造成短路,而因为大电流损伤芯片。由于目前半导体电路设计密度越来越高,电压或电流的瞬间变化对于芯片的损伤也越趋严重。此外,目前半导体业界部分认为客退品中经常出现的EOS (Electrical Over Stress) 问题与闩锁测试有相当程度关联,因此此项测试变得非常重要。

测试标准

闩锁测试主要参考JEDEC 78规范以及AEC-Q100-004之定义,其中在车用电子的测试中,定义必须使用Class II,即最高环境温度条件 (Maximum Operation Temperature),较传统常温更为严格。

CTI华测检测提供完整的半导体产品芯片可靠性试验项目,协助客户通过JEDEC、MIL—STD、AEC-Q等可靠性国际试验标准。

服务优势

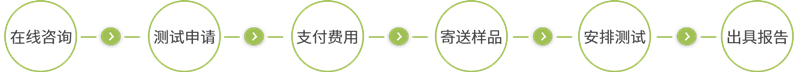

服务流程

免费获取更多专业咨询

常见问题

Q1:

实验多久后可以取得报告?

正常周期5~7个工作日,如需加急,请与业务联系。

Q2:

是否可以提供实验设计方案?

- 热线电话

- 业务咨询

- 快速询价

- 在线客服

- 报告验证

在线下单

在线下单