芯片老化寿命试验

提供完整的芯片产品老化寿命试验项目,协助客户通过JEDEC、MIL—STD、等可靠性国际试验标准

提供完整的芯片产品老化寿命试验项目,包含技术整合咨询、实验设计规划、硬件设计制作、可靠性试验、寿命预估等一站式服务,协助客户通过JEDEC、MIL—STD、AEC-Q等可靠性国际试验标准。

服务背景

半导体产品是电子产业的核心,而其可靠度试验的关键项目在针对芯片老化寿命,实验项目最普遍是以JEDEC 47或MIL-STD 883为基础进行。根据JEDEC 47的建议,样品的取得是必须三个非连续生产批次,以模拟生产的稳定度,并可参考Family概念适度减少实验项目与样品数。

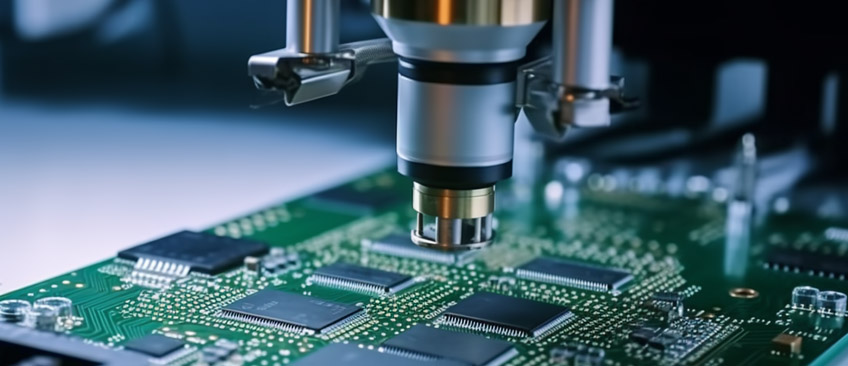

多数的老化寿命试验,必须透过老化板作为测试机台与芯片的接口。老化板是整个试验的核心,必须确保其稳定性,避免衍生额外问题。

芯片老化寿命试验

1.检测项目

正文:我们提供的测试项目一共分为3小点

1).高/低温寿命试验

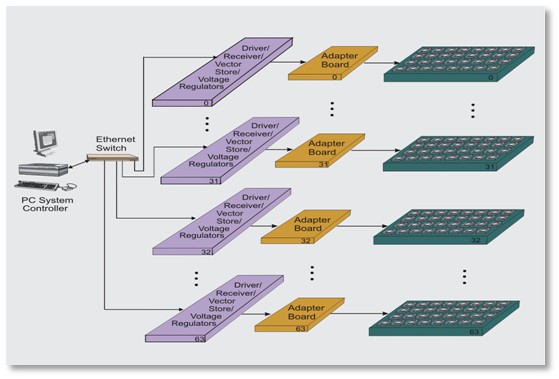

芯片透过高/低温寿命试验,以仿真在不同温度下的加速老化状态,常用的加速因子有电压、电流、温度与湿度等项目。高低温寿命试验的温度规格是参考芯片的结温 (Tj,Junction Temperature),高温一般消费型与工规产品使用125℃,低温则使用50℃。寿命试验的测试时间以1000小时为基础,实际的测试时间必须根据客户产品保固期,使用寿命公式进行推估。寿命试验属于动态试验,除了上述的加速因子外,通常会输入特定的程序,在动态的环境中确保芯片无任何的异常超标现象,以更贴近客户使用的环境。下图为老化测试设备的架构图。

2).早夭失效率试验

早夭失效率的试验目的针对特定或特殊产品,例如车用产品,进行一个放大量的观察。早夭失效率试验的另一个重要目的在针对产品进行出货后的使用寿命进行估算,以确保产品稳定度以及需要准备多少的备品作为后续RMA之用。实验的条件与实际寿命试验相同,但测试时间较短,且测试后无异常之产品可以出货。下图为浴缸曲线中的早夭区,可以看出早夭的问题来自制造与测试筛选不足而流出,是观察生产良率相当重要的一项测试方式,而非仅以功能测试(FT)结果为主。

3).高温储存寿命试验

4).非挥发性内存寿命试验

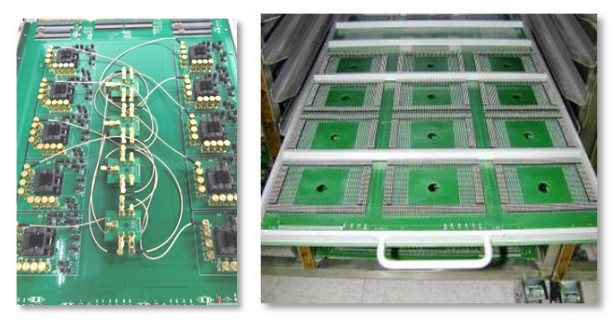

5).老化板硬件设计与制作

老化板的设计制作是整个寿命试验的关键。不同的产品类别与应用,衍生的频率、传输速度、讯号完整度、发热现象、阻抗匹配(Impedance)等,在老化板的设计、材料选择、结构等考虑上相对复杂。蔚思博检测是目前唯一可以提供老化板设计制作一条龙服务的公司,在考虑成本下,根据产品规格可选择适当之万用板(Universal Board),制作小板DUT Card解决,或者根据成本考虑设计专板等。此外,华测蔚思博检测也是唯一一家能够提供RF硬件设计与试验的第三方实验室。

2.样品水平

可靠度寿命试验的抽样方式采取最低允收水平LTPD (Lot Tolerance Percent Defective),信心水平(Confidence Level)一般使用90%。样品数的选择与信心水平均影响到寿命的预估值,必须非常注意。

服务优势

CTI华测检测在芯片寿命试验,拥有在半导体制程与应用领域具有多年经验的专业人员,可根据客户需求提供定制化服务。

目前已在上海张江、上海金桥、上海浦江、合肥、中国台湾新竹设立五大半导体测试及分析实验室,实验室总面积1万多平方米,搭建了完整的检测平台服务,具备CNAS、ISO9001、ISO17025、ISO27001、ANSI/ESD S20.20等资质。

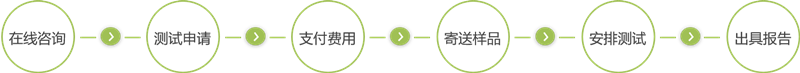

服务流程

Q1:

实验多久后可以取得报告?

正常周期5~7个工作日,如需加急,请与业务联系。

Q2:

是否可以提供实验设计方案?

- 热线电话

- 业务咨询

- 快速询价

- 在线客服

- 报告验证

在线下单

在线下单